# ANNUAL REPORT 2019

# TABLE OF CONTENTS

| Chairman's Message           | 03 |

|------------------------------|----|

| Executive Director's Message | 06 |

| About Us                     | 08 |

| Vision and Mission           | 08 |

| Research Pillars             | 09 |

| 2019 Highlights              | 10 |

| Research Overview            | 12 |

| High Speed Transceivers      | 13 |

| Precision Circuits           | 14 |

| Power Management             | 15 |

| Digital                      | 16 |

| Current Members              | 17 |

| IP Register                  | 18 |

| Researcher Profiles          | 23 |

| Dr. Ivan O'Connell           | 25 |

| Prof. Peter Kennedy          | 38 |

| Prof. Bogdan Staszewski      | 45 |

| Prof. Anding Zhu             | 55 |

| Dr. Teerachot Siriburanon    | 61 |

| Dr. Elena Blokhina           | 62 |

| Dr. Deepu John               | 63 |

| Mr. Seamus O'Driscoll        | 67 |

| Dr. Padraig Cantillon Murphy | 74 |

| Dr. Barry Cardiff            | 77 |

| Dr. Brendan Mullane          | 79 |

| Dr. Darren Francis Kavanagh  | 82 |

| Dr. Emanuel Popovici         | 85 |

| Alumni                       | 86 |

| Research Publications        | 88 |

## CHAIRMAN'S MESSAGE

The Microelectronic Circuits Centre Ireland (MCCI) has a unique relationship with Tyndall National Institute. Enterprise Ireland and IDA. The on-going collaboration and specialist ecosystem that has been developed allows a team of world-class researchers and postgraduate students to deliver excellent application driven research. This has contributed to positioning Ireland as a global location for microelectronics companies, thereby contributing hugely to the vibrant microelectronics industry.

The Irish Government, through Enterprise Ireland and IDA, are investing significant funding and resources into the centre. It is recognised that MCCI gives existing indigenous companies a large competitive advantage as well as helping in the creation of new start-up companies. The end result being an increase to indigenous employment and export revenue. MCCI has become the de-facto conduit for IDA clients entering the Irish microelectronics system, and we are very encouraged by the number of semiconductor companies establishing or expanding their circuit design R&D operations in Ireland.

One of the key success of the centre is how it has become a source of talented and experienced researchers for industry, know-how and industry relevant IP, which give a competitive advantage to our members leading on to increased revenue, profit and employment. This is evidenced in the researcher profiles and IP that are featured in this year's report, these are the future leaders who will bring the sector to the next level in terms of employment and contribution to GDP. MCCI member companies employ almost 13,000 people in high value jobs, a 14% growth in employment from 2018. There is also a strong indigenous sector which has in the past number of years has seen VC investments of over €184M and exits over €100M.

MCCI has become the go-to place for industry to carry out research with academia for microelectronics, and will continue to focus on microelectronics circuits servicing the €9B export industry in Ireland. It is no coincidence that some member companies have strengthened their R&D presence in Ireland as a result of collaborating with MCCI, which is a huge achievement. The centre has ambitious plans in place to scale, which will undoubtedly lead to further enhancing Ireland as a leading country for attracting foreign direct investment and new microelectronics start-ups.

Donal Sullivan Chairman

## **EXECUTIVE DIRECTOR'S MESSAGE**

As a centre, we are well established as a single point of contact for access to high calibre experts in the field of microelectronics. Hosted in Tvndall National Institute, our team consists of almost ninety researchers and engineers six research institutions. across collaborating on over fifty projects. The team profiles featured in this report are testimony to the calibre of talent in MCCI. The report aims to showcase the scope and depth of the research we are engaged in. The changes year on year demonstrate the pipeline of talent that has transferred to Irish industry. Central to our success is our people who consistently work to deliver world class research outcomes.

Over the next five years we will continue to grow and scale the centre, to realise our vision to be a world leading Microelectronic circuit's research centre. I am pleased to report that after extensive consultation and engagement with our members in 2019, we have submitted a funding proposal to Enterprise Ireland for the next phase of MCCI. Negotiations are at the final stages and I anticipate sharing the positive outcome very shortly.

Microelectronic circuits are a key enabling technology, which are fundamental to, and underpin all electronic systems, and this research is central to the advancement of this sector. Despite 2019 being a down year for semiconductors, by the end of 2019 we are seeing a recovery begin as the global industry sees strong growth return, driven by changing technology cycles and market drivers. At the time of writing the Coronavirus pandemic is unfolding, and having a dramatic impact not just on our sector but across the world. As a centre we have adapted exceptionally well, completing a number of tapeout during that transition. This resilience is characteristics of the centre and the attitude of our people. As the impact of Coronavirus is fully realised in the coming year, we have a greater responsibility than ever to support our industry partners, as we get the whole sector moving again.

We are in a unique position to bridge the gap between industry and academia to move apace with industry growth. Two of the major industry growth drivers have been the proliferation of complex electronic devices especially in automotive and medtech applications, and the growing amount of semiconductor content per device. Electronic products are becoming more complex, and with a growing level of semiconductor content. Our growth plans are

consistent with national strategies such as Innovation 2020, the National Development Plan 2018-2027 and Future Skills Needs 2017-2022 where we will continue to excel at meeting the critical needs of industry.

The content of this report showcases the level of expertise from our professors, principal investigators, senior researchers and students who consistently work on ground breaking circuit research. By providing our world-leading research, we provide competitive advantage to microelectronics companies (SMEs and MNCs) located in Ireland. Ultimately leading to increases in employment, export revenue and the generation of future leaders in the sector.

I would like to take this opportunity to thank our staff and students for their ongoing hard work and commitment as they work to make an impactful difference to the sector through their research. The continued growth and success of MCCI is due to their expertise and unique skillset to deliver innovative ground breaking research for industry.

Donnacha O'Riordan Executive Director

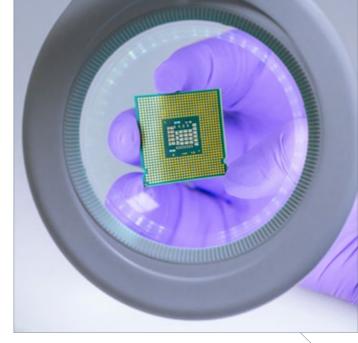

## **ABOUT US**

The Microelectronic Circuits Centre Ireland (MCCI) was founded to deliver high impact research for the semiconductor industry. Funded by Enterprise Ireland and the IDA, the role of MCCI is to generate innovative technologies. MCCI acts as a single point of contact for the microelectronics industry in Ireland to access academic research. The centre has an annual research revenue in excess of €8.1million and a team of over 90 researchers and engineers across Tyndall National Institute, UL and UCD, collaborating on more than 50 research projects.

MCCI undertakes collaborative projects in the microelectronics circuit design space with an emphasis on mixed-signal, Analogue and RF circuits. Projects may have algorithm, digital design, IC architecture or system architecture components to them where these can lead to improved performance of mixed-signal circuits.

## **VISION AND MISSION**

To be the number one microelectronic circuits research centre globally, for industrial and academic collaboration by 2025.

To deliver high impact research outcomes, and by doing so develop our researchers into independent thinkers and future leaders in Irish companies and in the global semiconductor landscape.

# **RESEARCH PILLARS**

High Speed Transceivers

Power Management

Precision Circuits

Digita

# **APPLICATIONS**

Future Networks Communications & IOT

Sustainable Living

Medical Devices

Diagnostics

Health & Independent Living

Smart Sustainable Food Production Processing

## 2019 HIGHLIGHTS

## Feb 2019

Prof. Peter Kennedy, Scientific Director MCCI presented at ISSCC

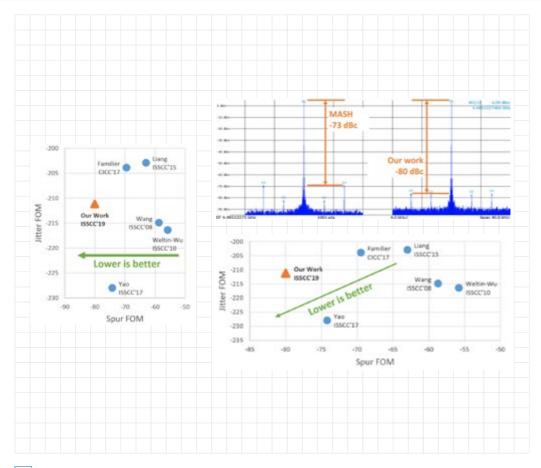

Our Scientific Director, Professor Michael Peter Kennedy presented his paper on "4.48GHz 0.18µm SiGe BiCMOS Exact-Frequency Fractional-N Frequency Synthesizer with Spurious-Tone Suppression Yielding a -80dBc In-Band Fractional Spur " at The International Solid - States Circuits Conference ISSCC.

## May 2019

MTC - MCCI Technical Conference was held at the Engineering & Material Science Centre in University College Dublin.

MCCI's Technical Conference is an annual event where we examine key microelectronic trends and novel academic papers. The event is a private event for our industry partners and research teams to gain insight and knowledge. There were four sessions on

- RF and PA Design

- Frequency Synthesis

- Data Converters

- Analog Circuit Techniques

The conference provides our members with access to novel information, key insights, and direct access to microelectronic research experts. The event is of very high value to our members as they will gain advance insight to our research breakthroughs.

### September 2019

MCCI attend the National Ploughing Championships in Fenagh, Co. Carlow

Members of the team went to the National Ploughing Championships to showcase the first prototype of "Bovisense", an on-farm diagnostic kit. The system is an innovative point-of-care bovine disease diagnostics system for vets, which diagnoses a range of IBR related viruses within 15 minutes. A multi-disciplinary team led by MCCI in collaboration with the Nanotechnology group from Tyndall National Institute are working to commercialise the product to bring it to market.

They won a Certificate of Achievement for being a finalist in the Innovation Arena.

## November 2019

Engineers Ireland Awards

Matthew Agnew, Masters Student MCCI and Conor Healy, who was an Intern MCCI won prizes at the Engineers Ireland and Institution of Mechanical Engineers Awards 2019. They were awarded 2nd place in the Best Individual Applied Student Engineering Project competition. Matthew won in the postgraduate category while Conor won for the undergraduate category.

We host a range of webinars throughout the year to keep our industry partners up to date on the advances in our research.

| Webinar Series                                                                                                                             | Speaker        |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Quantum Bits (Qubits) Implemented through Electrostatically Coupled Quantum Dots in Nanometer-Scale CMOS                                   | Elena Blokhina |

| An Adaptive-Resolution Quasi-Level-Crossing-Sampling ADC Based on<br>Residue Quantization in 28-nm CMOS                                    | Hongying Wang  |

| Intuitive Understanding of Flicker Noise Reduction via Narrowing of Conduction Angle in Voltage-Biased Oscillators                         | Yizhe Hu       |

| A 31-W, 148-fs Step, 9-Bit Capacitor-DAC-Based Constant-Slope Digital-to-<br>Time Converter in 28nm CMOS                                   | Peng Chen      |

| Challenges in On-Chip Antenna Design & Integration with RF Receiver Front-<br>End Circuitry in Nanoscale CMOS for 5G Communication Systems | Mahsa Hedayati |

| Panther - a High Precision sub 1V ADC in 28nm CMOS                                                                                         | Daniel O'Hare  |

| Passive Switched-Capacitor DS Modulator Based on Pipelined Charge-<br>Sharing Rotation in 28-nm CMOS                                       | Hongying Wang  |

| A 0.2-V 30-MS/s 11b-ENOB Open-Loop VCO-Based ADC in 28-nm CMOS                                                                             | Viet Nguyen    |

## **RESEARCH OVERVIEW**

Our research roadmap is centred around the delivery of innovations for the broad range of applications listed below. Microelectronics is a key enabling technology for all these applications and our aim is for all of our research to be world beating.

## Future Networks, Communications and IOT

- Beyond 5G cellular infrastructure for mobile phone technology.

- Satellite and mmWave communications.

- OptoElectronics and PICs.

- Ultra-low Power Radio.

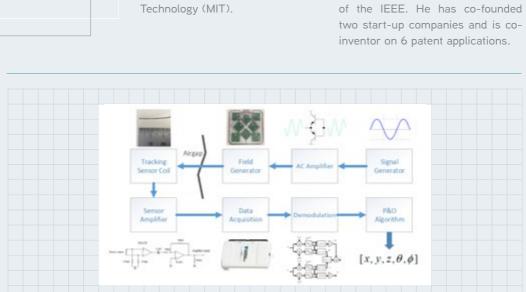

## Medical Devices & Technologies and Connected Health

- RF sensing namely depth, distance and composition.

- Biosensing and neuromodulation.

- On-body wearable and in-body implantable.

- Point of care, imaging and robustness.

## Smart Agri, Industrial and Automotive

- · Smart Agri, and animal diagnostics.

- Sustainability and water quality.

- Green Energy battery monitoring, health and charging.

- Machine monitoring and fault tolerance.

- Radar and antenna.

## Digital and Processing

- · Quantum and cryogenic.

- Artificial intelligence, machine learning and edge processing.

- Security and cryptographic technologies.

Robotics navigation, sequencing engines and annealing processors.

12 MCCI Annual Report

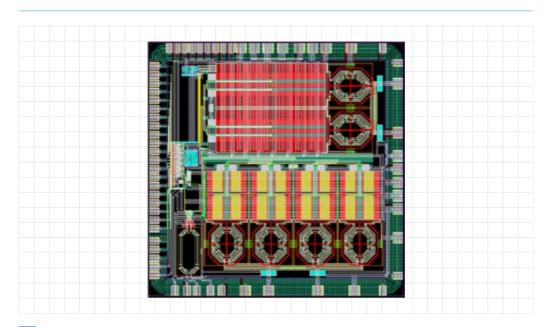

## HIGH SPEED TRANSCEIVERS

Our high-speed transceivers research pillar is focused on optical transceivers, mm-wave transceivers & systems, Hybrid RF Systems, and Hybrid GaN/CMOS/MEMs System-In-Package.

Our researchers are addressing the challenges that our industry partners need to enhance next-generation products. The increasing demand for broadband and 5G communications, with the use of massive multiple input and output (MIMO) and mm-wave technologies, drives demand for research in this space. The exponential growth of IoT, with sensing and imaging applications at sub-mm-wave frequencies being a key driver, allows us enhance performance and efficiency in these applications. Demand for faster wireless-data rates, within the context of mobile-battery limitations, drives the development of high-throughput and power-efficient transceivers.

An example of one of our collaborations enables a widespread deployment of devices and sensors utilizing existing cellular infrastructure. In this instance we are working on a beyond state-of-the-art solution in per bit efficiency for high data rate, low frequency transceivers.

Another ground-breaking project is the design of a high-performance chip for 5G applications

which aims to achieve higher resolution and lower power consumption. The objective is to enable cost reduction and enhanced battery life. The efficiency we can expect to obtain will be more than 35%. The benefits for end applications is the higher circuit integration level suitable for mobile devices, which delivers higher power efficiency and better battery performance.

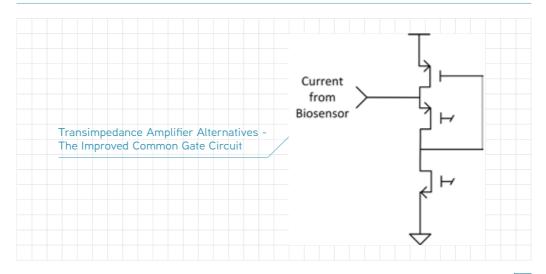

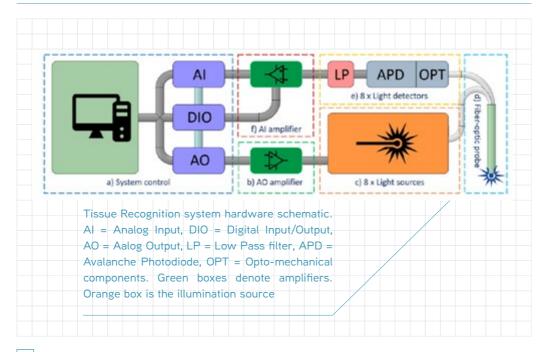

In the bio-photonics research space, we deal with diffuse light within tissue. Light is absorbed and scattered depending on the wavelength and tissue properties. The deeper we image in tissue the smaller and more complex the optical signal becomes. Optical detectors are often pushed to the limits of detectability. The overall detection system is also heavily dependent on the interface electronics to the detector and its location. Optimisation demands new levels of integration requiring co-location of the TIA, wide dynamic range, AGC, and communications. The research challenge at this level of integration is achieving a beyond state-of-the-art optical detector interface circuit and system design, which will enable more sensitive measurement in tissue. If successful this will assist clinicians to image and measure critical medical parameters, improving the quality of patient care.

## PRECISION CIRCUITS

Our precision circuits pillar is centred on the delivery of state-of-the art data converters and analogue front ends. There is a specific focus on sensor interface circuits, targeting applications including Smart Agri and point-of-care diagnostics. We work on capacitive and resistive sensor interfaces and time-based converters. Key research challenges include increased precision, noise immunity, increased bandwidth and linearity, and power efficiency, as measured in energy per conversion step.

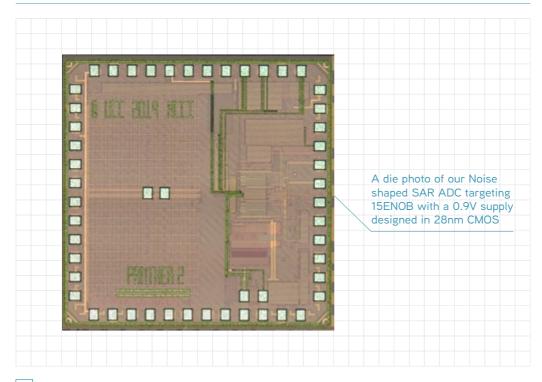

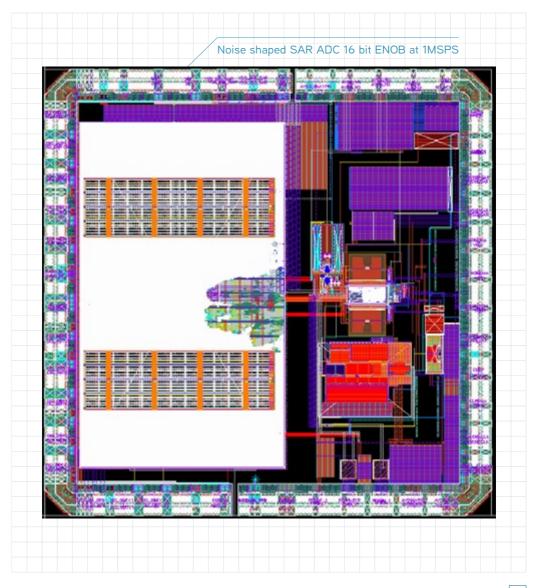

We are developing noise-shaped SAR ADCs in 28nm CMOS, which are implementing novel architecture and circuit techniques to increase precision and mitigate noise. We are also leveraging a host of new sensing methodologies that have emerged in electrochemistry and biological sensing over the past decade.

Noise-shaping techniques are shown to increase the resolution by two effective number of bits. The key blocks in SAR ADCs are capacitors, comparators, timing logic and processing logic all of which benefit from faster CMOS technologies. The objective of this is to leverage this speed advantage through oversampling and noise-shaping to achieve an ADC with greater precision. An important research driver in this space is improving on state-of-the-art in figureof-merit and PPA (power performance area) of the circuits. We have already developed some of the best performing SAR ADCs from a power consumption point of view, with 10bits of resolution and a signal bandwidth of less than 1MHz. Future research aims to further

the state-of-the-art in high-sensitivity current measurements at >10MHz bandwidth. In this regime, high AFE noise in the presence of large sensor capacitance is the limiting factor. Hence the research aims to use circuit techniques to mitigate this high AFE noise which has traditionally limited similar current readout solutions.

We work on ultra-low power and sub-threshold voltage research projects. Further advancements in the state-of-the-art are necessary for future Biomedical, IoT and Smart Agri based applications. Such ADCs typically target sub 1kHz sampling rate and 12-16 bit resolution. Initial focus is on developing ADCs with a power consumption target of less than 1 $\mu$ W and a Schreier FoM of 180+ dB. Secondly we can target reducing the leakage current, reducing the start-up time that the circuits require, improving the duty cycle efficiency, and extending the resolution achieved.

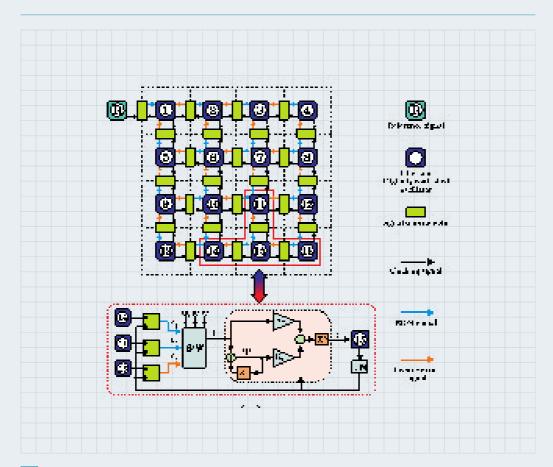

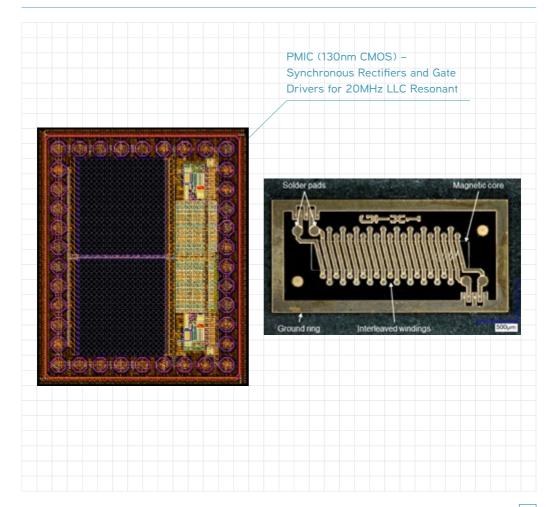

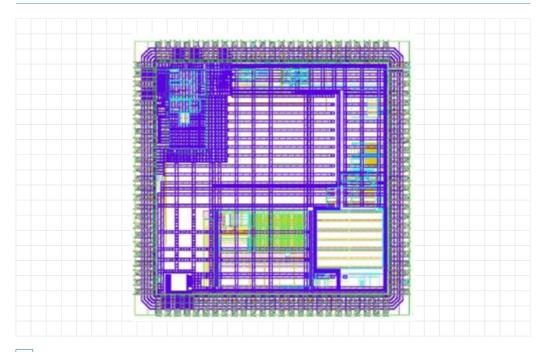

## POWER MANAGEMENT

Our research focus in power management is on highly integrated conversion, for example reducing the size and the need for external discrete components, and on energy harvesting – managing the source and storage of multiple micropower sources.

We are looking at the emerging area of hybrid and resonant switched-capacitor topologies that deliver better utilization of active semiconductors and passive components. We are presently developing highly integrated conversion to improve electromagnetic interference, efficiency and reliability. Energy harvesting projects include the development of integrated voltage regulation and novel topologies.

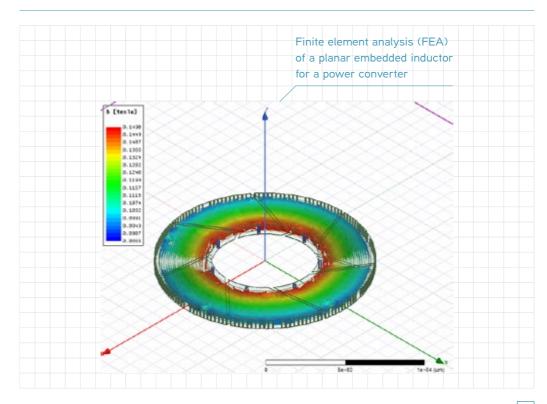

One of our research projects is exploiting advanced integrated magnetics for mobile and portable device point-of-load (3-7V POL) conversion. The objective is the removal of large external discrete chip inductors, transitioning to a much more highly integrated power system-in-package or in-die.

The research goal is granular power, where the performance of mobile SoC voltage regulation (high dynamic performance 1.8V to Core & IO voltages) becomes much more highly integrated and segmented to multiple voltage domains, enabling a multi-fold increase in battery life, dynamic performance and across-die thermal gradients.

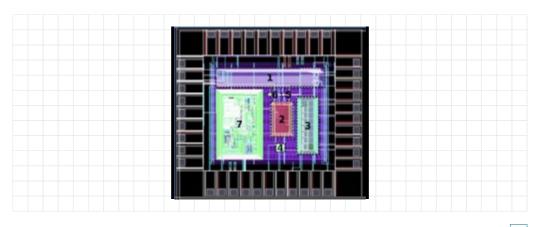

## **DIGITAL**

Within IoT applications, as security moves from being an add-on algorithm to a hardware solution implemented at the circuit level, circuits for cyber security has emerged as a key enabler. Secure-by-design is the overarching research output where safety is critical in operation in industrial control, public welfare and other applications.

Crypto circuit implementation, true RNG and private data security, where AI training features are integrated at the edge device, are all current areas of research interest. Improving energy efficiency and higher throughput become even more important as we implement NPUs (Neural Processing Unit) on edge devices, where our key metrics are Energy per Inference and Inference per Sec.

Physically tamper proof and Intellectual Property (IP) protection against reverse engineering are two examples of current research in this space, as the industry is increasingly concerned with

the growing risk of supply chain contamination by counterfeit devices.

The scope of our research also extends to efficient architectures and implementation of arithmetic functions approximation-based stochastic computing, as alternatives to binary computing for a number of low-power embedded systems. We are also looking at exploiting technology features, such as body biasing and passive device advancements, as we work to improve PPA (power, performance, area) of digital circuits.

Quantum engineering is an emerging field we are committed to addressing, initially looking at cryogenic temperature circuits, and the behaviour of CMOS circuits at cryogenic temperatures. Research is underway to examine circuits to control and observe quantum devices, ultimately addressing quantum computing applications.

## **CURRENT MEMBERS**

# IP AVAILABLE FOR LICENSING

| Description                                                                                                                                                       | Owning PRO | Research Lead   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|

| A 100dBFs SFDR Band-Pass $\Sigma\Delta$ Current-Steering DAC in UMC 90nm                                                                                          | UL         | Brendan Mullane |

| 0.32mm², 0-6GHz, 4ps rms Multi-band LC VCO PLL                                                                                                                    | NUIM       | Ronan Farrell   |

| A continuous time front end for ADC in 28nm SOI                                                                                                                   | UL         | Tony Scanlan    |

| 0.35μm CMOS Instrumentation Amplifier                                                                                                                             | UCC        | Ivan O'Connell  |

| 0.35µm CMOS nano-watt 32.768KHz always-on clock generator                                                                                                         | UCC        | Ivan O'Connell  |

| 0.35µm CMOS nano-watt 12b SAR ADC utlizing a 32KHz clock & converting at 800Hz                                                                                    | UCC        | Ivan O'Connell  |

| 0.35µm CMOS nanowatt differential input & output bandpass filter                                                                                                  | UCC        | Ivan O'Connell  |

| Digital Control from Innovation partnership                                                                                                                       | UL         | Mark Halton     |

| Digital Control synthesis tool from CFTD                                                                                                                          | UL         | Mark Halton     |

| 0.35µm CMOS thoracic impedance circuit used to infer respiratory rate                                                                                             | UCC        | Ivan O'Connell  |

| 0.35µm CMOS nanowatt voltage reference & bias current circuit. Vref is independent of temperature & power supply variation                                        | UCC        | Ivan O'Connell  |

| 0.35µm CMOS low power PMIC that uses an external inductor to increase a Vin (varying from 2V to 3V) to a higher Vout, programmable up to 18V.                     | UCC        | Ivan O'Connell  |

| 0.35µm CMOS Pacing Block which charges a Pace Capacitor via a current source. The Pace Capacitor is discharged in a controlled manner to force the heart to beat. | UCC        | Ivan O'Connell  |

| 0.35µm CMOS Neurostimulation pulse generator can operate up to 18 Volts, and delivers biphasic currents                                                           | UCC        | Ivan O'Connell  |

| 0.35µm CMOS Digital Block for controlling Pacing or<br>Neurostimulation                                                                                           | UCC        | Ivan O'Connell  |

# IP AVAILABLE FOR LICENSING

| -   | Research          | Category            | IP Block                                         | Description                                                                                                                          | Status            |

|-----|-------------------|---------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| RPO | Lead              |                     |                                                  |                                                                                                                                      |                   |

| UCC | Peter<br>Ossieur  | PAM-4 CDR           | Components<br>for analog<br>phase locked<br>loop | STM 65nm CMOS, Phase detector, charge pump, analog filter, high-speed digital divider circuit with few programmable divider settings | Silicon<br>Proven |

| UCD | Anding Zhu        | ADC                 | Algorithm                                        | Volterra-based RLS (Recursive<br>Least-Square) algorithms for Digital<br>Post-Correction of ADCs                                     |                   |

| UCD | Anding Zhu        | ADC                 | Algorithm                                        | Algorithms for Non-uniform Analog<br>Interpolated Multichannel Digital<br>Post-Correction for Time-Interleaved<br>ADCs               |                   |

| UCC | John Doyle        | AMS                 | Current Sense                                    | 0.35µm CMOS High-side Current<br>Sensor                                                                                              | Silicon<br>Proven |

| UCC | Kevin<br>McCarthy | Power<br>Management | DCDC                                             | 30MHz DC-DC Converter with Integrated Magnetics                                                                                      | Silicon<br>Proven |

| UL  | Tony<br>Scanlan   | ADC                 | ADC                                              | 65nm HiCOSANT SAR ADC with<br>Novel Calibration                                                                                      | Silicon<br>Proven |

| UCC | Peter<br>Kennedy  | PLL                 | Freq Div                                         | Divide-by-three Injection-Locked<br>Frequency Divider                                                                                |                   |

| UCC | Ivan<br>O'Connell | RF                  | Voltage<br>Controlled<br>Oscillator              | High-performance Voltage Controlled<br>Oscillators in a SiGe BiCMOS<br>technology                                                    | Silicon<br>Proven |

| UCC | Ivan<br>O'Connell | RF                  | Varactor                                         | High Q Varactor for High-<br>performance Voltage Controlled<br>Oscillators in a SiGe BiCMOS<br>technology                            | Silicon<br>Proven |

| UCC | Ivan<br>O'Connell | ADC                 | Thermal noise reduction                          | Reduction of Sampled KT/C Thermal<br>Noise for ADC                                                                                   | Simulation        |

| UCC | Ivan<br>O'Connell | AMS                 | TIA                                              | 3.3V 0.35µm transimpedance amplifier                                                                                                 | GDS               |

| UCC | Ivan<br>O'Connell | AMS                 | Active Quench<br>Circuit                         | Active quench circuit for use with Single Photon Avalance Diode                                                                      | GDS               |

| UCC | Ivan<br>O'Connell | AMS                 | Bandgap                                          | 3.3V supply 0.35µm 1.2V Bandgap<br>Reference circuit                                                                                 | GDS               |

| UCC | Ivan<br>O'Connell | Digital             | Ring Oscillator                                  | 0.35µm 666MHz ring oscillator with divide-by-32                                                                                      | GDS               |

| Owning<br>RPO | Research<br>Lead  | Category   | IP Block                               | Description                                                                                                                                                                                                                                                  | Status            |

|---------------|-------------------|------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| UCC           | Ivan<br>O'Connell | AMS        | SPAD readout                           | $0.35 \mu m$ single photon avalance diode pixel read out circuit                                                                                                                                                                                             | GDS               |

| UCC           | Ivan<br>O'Connell | AMS        | TDC                                    | 0.35µm time-to-digital converter                                                                                                                                                                                                                             | GDS               |

| UCC           | Ivan<br>O'Connell | Digital    | Standard-cells                         | 0.35µm digital standard cells                                                                                                                                                                                                                                | Layout            |

| UCC           | Ivan<br>O'Connell | Biomedical | Pace<br>controller<br>circuit          | 0.35µm CMOS low power Cardiac<br>Pace Controller which interfaces with<br>sense channels & microprocessor to<br>handle multi-mode pacing                                                                                                                     | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell | Clocking   | Clock<br>generator                     | 0.35µm CMOS low power clock<br>oscillator that generates a freq stable<br>across power supply range, with<br>adjustable pulse width                                                                                                                          | Silicon<br>Proven |

| UCC           | Ivan<br>OʻConnell | Biomedical | Chip                                   | 0.35µm CMOS low power chip that includes Atrium Sense, Ventricle Sense, Thorasic Impedance Sense, Atrium Pace, Ventricle Pace, Neurostimulation, Hysteric Boost Block and Real time Clock to enable Rate Responsive heart pacing                             | Silicon<br>Proven |

| UCC           | Ivan<br>OʻConnell | Biomedical | Chip                                   | 0.35µm CMOS low power chip that includes Atrium Sense, Ventricle Sense, Atrium Pace, Ventricle Pace, Neurostimulation, Hysteric Boost, Real time Clock and Pace Controller to enable heart sensing and pacing without the intervention of a micro controller | Silicon<br>Proven |

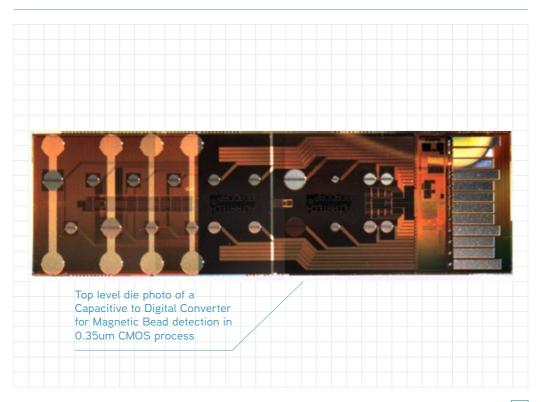

| UCC           | Ivan<br>O'Connell | ADC        | Capacitive-<br>to-Digital<br>converter | 0.35µm CMOS Oversampled Sigma<br>Delta ADC with extended Input Range                                                                                                                                                                                         | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell | Digital    | Asynchronous<br>I2C Slave<br>Interface | Asynchronous I2C Slave Interface                                                                                                                                                                                                                             | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell | Sensor     | Layout                                 | Several permutations of Interdigitated<br>Sensor Structure Test Chip                                                                                                                                                                                         | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell | ADC        | Sigma Delta<br>Modulator               | Sigma Delta Modulator on XFAB<br>0.35µm                                                                                                                                                                                                                      | GDS               |

| Owning<br>RPO | Research<br>Lead     | Category   | IP Block           | Description                                                                                                                                                                                                                                                                       | Status            |

|---------------|----------------------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| UCC           | Ivan<br>O'Connell    | Biomedical | DNA Sensor<br>Chip | 0.35µm CMOS DNA Sensor Chip containing a high-resolution sigmadelta Capacitive-to-Digital converter, I2C Interface, bandgap reference, bias generator, 1MHz oscillator, Power-on-Reset circuits, EEPROM memory for ID coding, chip tracking, and sensor calibration coefficients. | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell    | ADC        | SAR ADC Chip       | 28nm 13 ENOB noise-shaped SAR<br>ADC                                                                                                                                                                                                                                              | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell    | ADC        | SAR ADC Chip       | 28nm 15 ENOB noise-shaped SAR ADC                                                                                                                                                                                                                                                 | GDS               |

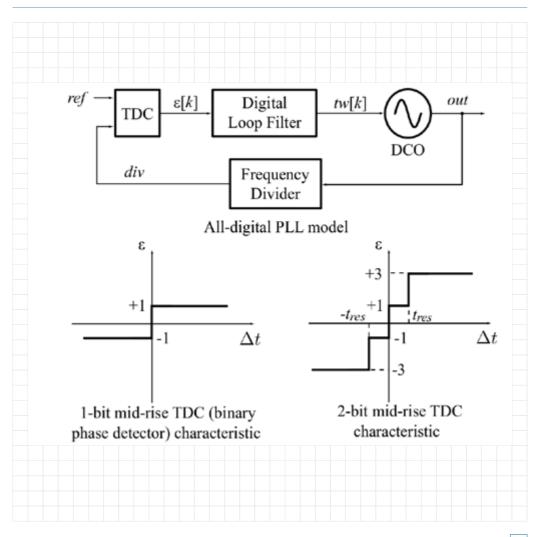

| UCC           | Mark<br>Smyth        | Clocking   | ADPLL              | 28nm 16GHz Low Power All-Digital<br>Phase Locked Loop (DPLL)                                                                                                                                                                                                                      | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell    | ADC        | SAR ADC Chip       | 65nm Low Power 1MS/s 12-bit SAR<br>ADC, 76db SFDR, 62db SNR                                                                                                                                                                                                                       | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell    | ADC        | SAR ADC Chip       | 130nm 2-MS/s 12-bit Extended Input<br>Range SAR ADC with Improved DNL<br>& Offset Calculation                                                                                                                                                                                     | Silicon<br>Proven |

| UCC           | Ivan<br>O'Connell    | ADC        | High-speed<br>ADC  | 28nm 1GS/s 8-Bit ADC                                                                                                                                                                                                                                                              | Layout            |

| UCC           | Bogdan<br>Staszewski | RF         | RF-DAC             | 28nm iDTX - an Interpolative Digital<br>Transmitter with Quantization Noise<br>and Replicas Rejection                                                                                                                                                                             | Silicon<br>Proven |

# **OUR RESEARCH LEADERS**

Dr. Ivan O'Connell

Prof. Peter Kennedy

Prof. Bogdan Staszewski

Prof. Anding Zhu

Dr. Teerachot Siriburanon

Dr. Elena Blokhina

Dr. Deepu John

Mr. Seamus O'Driscoll

Dr. Padraig Cantillon Murphy

Dr. Barry Cardiff

Dr. Brendan Mullane

Dr. Darren Francis Kavanagh

Dr. Emanuel Popovici

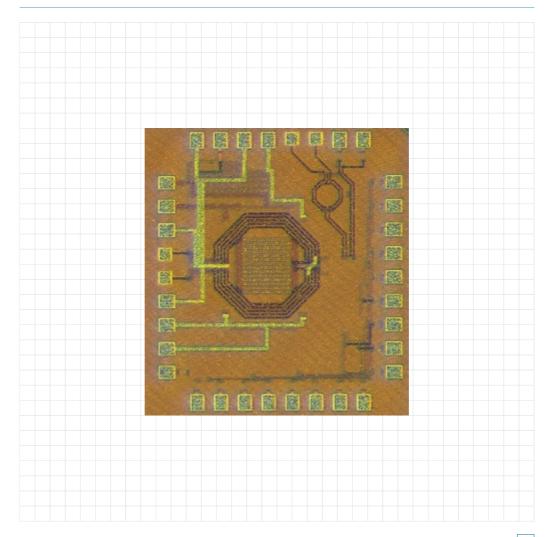

## Dr. Ivan O'Connell, Head of Precision Circuits

Ivan joined MCCI in 2013 and is the Head of Group of the MCCI core research team. Since joining MCCI he has grown the MCCI core team to 20 researchers, which consists of Masters and PhD students, Postdocs, Research Assistants and Senior Researchers. His primary research interests are in the area of Analogue Mixed Signal Circuits and data converters. He is particularly interested in the application of this research in areas including: Internet of Things, Biomedical, Smart Agri and Energy Harvesting. He is currently a principal investigator in a number of Innovation Partnerships and Commercialisation Funds. He is involved in a number of H2020 projects. In addition, he is an SFI CONNECT Funded Investigator and is actively involved in the newly

funded SFI centre VistaMilk. Prior to joining MCCI, Ivan was the Design Manager in ChipSensors, which was subsequently acquired by Silicon Laboratories in 2010. While there, he lead the development of their digital relative humidity and temperature sensor products, from initial concepts, through to initial and interim prototypes, to their subsequent commercialisation. including custom test development. Since joining MCCI, he has secured €6 million in funding, in addition to 10 commercial licenses and transferring 27 trained researchers to industry. Since 2016, he is a member of the Custom Integrated Circuits Conference Technical Programme Committee.

## Dr. Daniel O'Hare, Senior Researcher

Daniel O'Hare received the BE degree in Electronic Engineering from University College Dublin in 2000 and completed his PhD at the University of Limerick in 2017. He joined Motorola Semiconductor 2000 and from 2004 to 2008 he was with Freescale Semiconductor designing ADCs and DACs for Cellular transceivers. From 2008 to 2012 he was Analogue Design lead with M4S NV a spinout of IMEC and from 2013 to 2017 he was an ADC researcher in the Circuits and Systems group at the University of Limerick. Since 2017 he is a Senior Researcher in MCCI based at the Tyndall National Institute. He lectures 'Advanced Analog IC Design' to UCC masters in Electronic Engineering students.

Current research: Danny's present research is in precision ADCs and low-noise sensor interface circuits. He is design lead/architect of the MCCI precision Noise shaped SAR project. He is also supervising Postgraduate research projects investigating precision current interfaces capable of detecting currents with pico-ampére precision. He has several on-going projects with the Bio-photonics group at Tyndall National Institute.

Research Topics: Danny's research interests are low noise, area and voltage analogue interface circuits and ADCs. These interests are applied in Sensor interface ICs with precision current sensing interfaces a strong interest.

## Anita Schuler, Senior Digital Design Engineer

Current Research: 1.5GHz Noiseshaped SAR ADC on TSMC 28nm

Implementation of an ADC Non-Linearity Calibration Algorithm in the Xilinx Zynq UltraSca

Research Topics: Digital design for ADCs, including specification, design, Verilog RTL Coding, verification, synthesis, place and route and gate-level back-annotated simulations.

Digital PLL on TSMC 28nm

Digital-on-Top auto-routing using Cadence Innovus

Verilog and Digital Design consulting to other groups in Tyndall/UCD

Education: Anita holds a B. Eng (Electronic Engineering), University of Limerick, 1994. First Class Honours.

Work Experience: Anita previously worked as a Digital Design Engineer in Silicon and Software Systems (S3) in Dublin. She then moved to Galway and worked as a Senior Digital Design Engineer for Toucan Technology, which was later acquired by PMC-Sierra.

She also worked as an FPGA Design Lead for a start-up company called PortoMedia.

## Dr. Gerardo Salgado, Senior Researcher

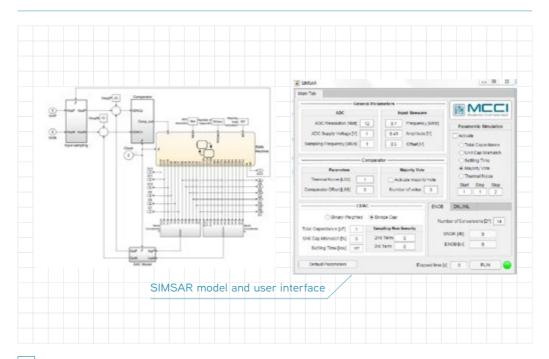

Current research: He is developing novel high resolution Analogto-Digital Converter (ADC) architectures using digital signal processing techniques compensate for analog circuit imperfections. He is also continuously developing/improving his Matlab(R)-based SAR ADC design toolbox, SIMSAR, which provides accurate simulation results at a highly reduced computational time. The SIMSAR toolbox is available to download free from charge at https://www.mcci.ie/ simsar-toolbox/. (This toolbox has been already downloaded over 100 times from different universities around the world.)

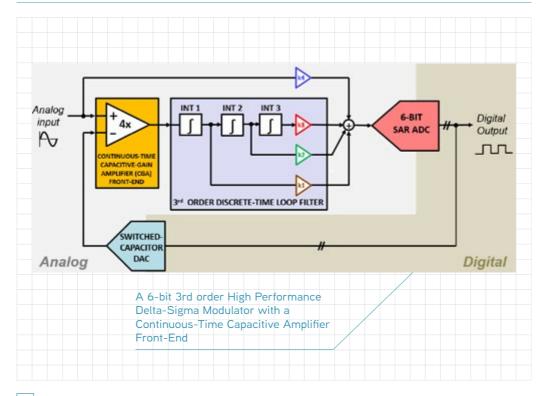

Research topics: Design and implementation of SAR ADCs, Delta-Sigma Modulators (Digital,

Discrete-time and Continuoustime), Digital Signal Processing (Filter design), Machine-Learning assisted calibration and simulation algorithms for ADCs, Behavioural modelling, and Computer-Aided-Design tools.

Education: Gerardo Salgado received the B.S., M.S and Ph.D. degrees in Electronics Engineering form Institutes ITP and INAOE, Mexico, in 2009, 2011 and 2015, respectively. During his Ph.D. studies, he joined the Microelectronics Institute of Seville (IMSE), Seville, Spain, and Texas A&M University, USA, as a visiting scholar. Since January 2016 he has been working as a postdoc researcher at MCCI.

## Aidan Murphy, PhD Student

Current Research: As sensing technologies develop, there is an increase in the demand to take measurements at the point of sample. MCCI are collaborating with the Nanotechnology Group in Tyndall to enable point of care electrochemical sensor detection. A variety of voltammetric techniques have been enabled on the data acquisition system. Results have been accepted for publication at the International Instrumentation Measurement Conference. Houston, 2018 and IEEE Nano, Cork, 2018. The system is now battery powered and wireless connectivity has been enabled via Bluetooth. It can be interfaced to via an android smartphone application.

Current work is focused on enabling more electrochemical tests and miniaturising the system.

Current research is focused implementing portable impedemetric biosensing on nano electrochemical sensors.

### Research Topics:

- Embedded Systems

- Electrochemistry

- Nanotechnology

Education: Aidan received his BE degree in Electrical and Electronic Engineering from University College Cork in 2016 and is currently pursuing a PhD degree with MCCI, University College Cork

## Subhash Chevella, Senior Design Engineer

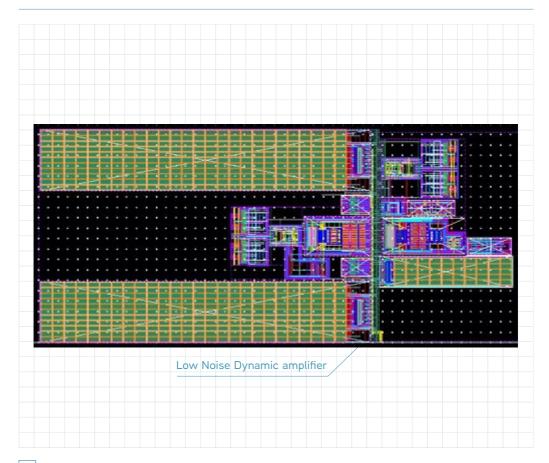

Current research: Current research involved in investigating the novel design ideas to improve the linearity and the noise for high precision analogue circuits. In addition, digitally assisted techniques to improve the performance of analogue engineering blocks.

Research topics: Low power techniques in deep-submicron technology

High speed, Low noise Dynamic amplifiers

High precision & Hybrid ADCs

Education: Subhash Chevella is a PhD researcher at MCCI. The Primary focus of his research is precision analogue engineering blocks.

He completed his Master's in 2011 from DA-IICT, India. His Masters research was involved in Analysis of Charge injection, Clock feedthrough and Capacitor mismatch in Switched Capacitor Circuits.

He completed his Bachelor's in Electronics and Communication in 2009 from JNTU, Hyderabad, India.

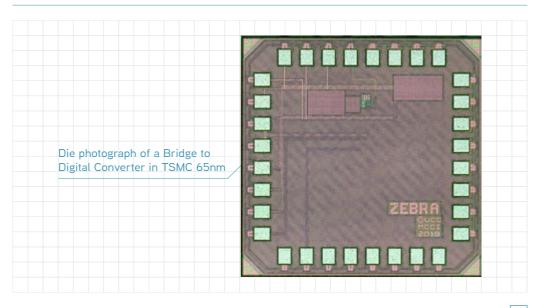

## Annamaria Fordymacka, PhD Student

Current Research: Temperature sensors are required in a vast number of applications such as food monitoring or MEMS compensation. Traditionally, the temperature sensor read-out circuitry would consist of a Wheatstone bridge followed by an instrumentation amplifier that would require high input impedance and low inputreferred noise. While the design of such an amplifier is challenging, the design of the subsequent analog-todigital converter (ADC) is equally if not more demanding, to ensure that these blocks do not limit the resultant achievable resolution and accuracy. There have been many attempts to remove the requirement the input instrumentation amplifiers from temperature-todigital converters, but the majority of these are based on either sigmadelta or VCO based ADC, which trade area for power. The research

here is on designing a more efficient architecture for a bridge-to-digital converter.

## Research Topics:

- Analog and Mixed-Signal IC Design

- Hybrid Data Converters

- Low Energy Applications

- Sensor Interfaces

Education: Annamaria graduated from UCC with a Bachelor's Degree in Electrical & Electronic Engineering in 2014. After her graduation, she joined MCCI at Tyndall National Institute where she completed her Master's degree in 2016. She is currently a PhD researcher in MCCI under the supervision of Dr Ivan O'Connell. The primary focus of her research is mixed signal/analogue IC design.

## Spyros Kalogiros, PhD Student

Spyridon (Spyros) is currently a Ph.D. Student / Researcher and a member of Microelectronic Circuits Centre Ireland (MCCI), part of Tyndall National Institute in Cork, Ireland. He received his B.E. degrees in Electronic Engineering Education and in Electronic Engineering, in 2010 and 2011 respectively, both from the School of Pedagogical and Technological Education in Athens, Greece, and his M.S. degree in Electronic Physics / Radioelectrology from the Physics Department of Aristotle University of Thessaloniki, Greece, in 2015. He has held internship positions with COSMOTE S.A. in Athens, Greece, as a broadband network engineering trainee

for the operation, maintenance and upgrade of its 3G mobile network, and with MCCI, where he has worked on an implantable and fully integrated biopotential acquisition chip, for cardiac pacing and sensing purposes. His current Ph.D. research is on the field of Delta-Sigma Analog-to-Digital Converters, aiming to develop new design guidelines and solutions for higher performance in terms of higher Figure-of-Merit, and therefore, to set higher state-ofthe-art specifications, as imposed by the ongoing and increasing demand for even more efficient Analog-to-Digital Converters over the next few years.

## Madhan Venkatesh, PhD Student

Current research: Developing low power and low voltage analog to digital converters on TSMC 65nm.

Research topics: low voltage and low noise comparator design, low power digital circuits, sampling circuits breaking the KT/C thermal noise Limit, SAR ADC'S.

Education: B.E. in electronics and communication from Visvesvaraya Technological University, Karnataka, India and is currently pursuing the PhD degree with MCCI, University College Cork

## Hao Zheng, Research Assistant

Current research: Implementation of high-resolution data converter in 28nm CMOS processes for IoT application.

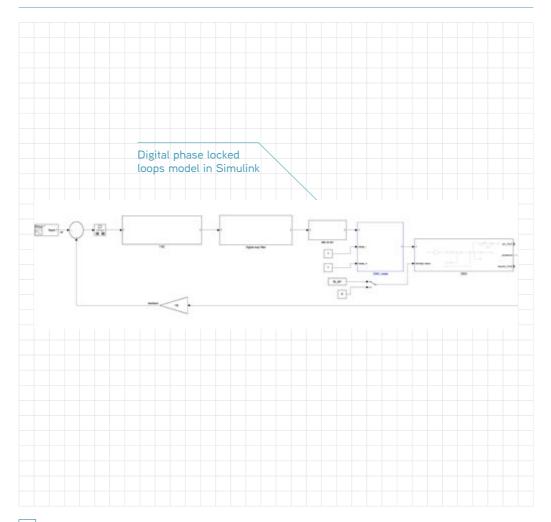

Building DPLL and noise model for the clock jitter research, based on Matlab and Simulink.

Analysis and research jitter suppression techniques for the high-resolution converter.

## Research Topic:

- · CMOS Analog IC design, Mixed-signal system modelling and design.

- DPLL & its noise modelling

Education: Master of Engineering Science, University College Dublin, Dublin, Ireland(2017)

Bachelor of Engineering, Lanzhou University of Technology, Lanzhou, Gansu, China(2013)

## Anthony Wall, PhD Student

Current Research: A host of new sensing methodologies have emerged in electrochemistry and biological sensing over the past decade. The physics of many of these sensing topologies require charge-based rather than potentialbased measurement. Thus there is a requirement for high resolution current-to-digital readout solutions, often in arrays. Anthony is researching the wide-bandwidth acquisition and digitization of current signals using novel Analogto-Digital conversion methods. Wide bandwidth current readout presents a host of challenges in terms of noise, bandwidth and power consumption. Anthony intends to exploit novel circuit architectures, such as the Flipped Voltage Follower Current Conveyor, to improve the state of the art in wideband Currentto-Digital conversion. MIDAS 3rd Level Project of the Year Winner for 'Design and Stimulation of an Analog Front End for Cancer Detection by

Fluorescence Imaging 'UCC School of Engineering Joe Gantly Prize Winner for design of Sigma-Delta Converter while on placement with Cypress Semiconductor

#### Research Topics:

- Current-Mode Sensor Interfaces

- High-Resolution Current Measurement

- Wide Bandwidth TIA Frontends

- Nanoscale Sensor Modelling

- Current-Mode ADC design

- Nanopore-based DNA Sequencing

Education: Anthony graduated from University College Cork with 1st Class Honors in the BE degree in Electrical & Electronic Engineering in 2018, and is currently pursuing the PhD degree with MCCI, University College Cork in the area of Mixed Signal Circuit Design.

## Rachel Georgel, Masters Student

Current Research: Combining the photodetectors electronic and interfaces together has many advantages especially in medical device applications, including custom sensor calibration, on chip data conversion and pre-processing and signal control and transmission. Hardware solutions to situate the electronics and photodiodes together can use Printed Circuit Boards (PCBs) technology to connect off the shelf detectors and electronic components, and this can be quickly realised. However, PCB based solutions have a large footprint and PCB wiring tracks pick up noise and parasitic wiring capacitances, which limits the speed of measurements. Hence, this is not an optimal solution to achieve the lowest overall noise,

detect the smallest signals and the most accurate time stamp. Rachel's project involves the design of ultralow noise high precision analogue and digital circuits as an application specific IC (ASIC) to electronically capture bio-photonics data. This involves working with the Biophotonics team to understand their system requirements and then design a custom Integrated Circuit chip(s) to meet those specifications.

Education: Rachel graduated from University College Dublin with a 1st Class Honours in the BE degree in Biomedical Engineering in 2019. She is currently pursuing a PhD degree with MCCI and the Bio-Photonics group in Tyndall, in the area of electronics interfaces for Bio-Photonics data capture.

# Michael Pastoril, Senior IC Layout Engineer

Education: Bachelor of Science in Electronics and Communications Engineering Polytechnic University of the Philippines Manila 1998.

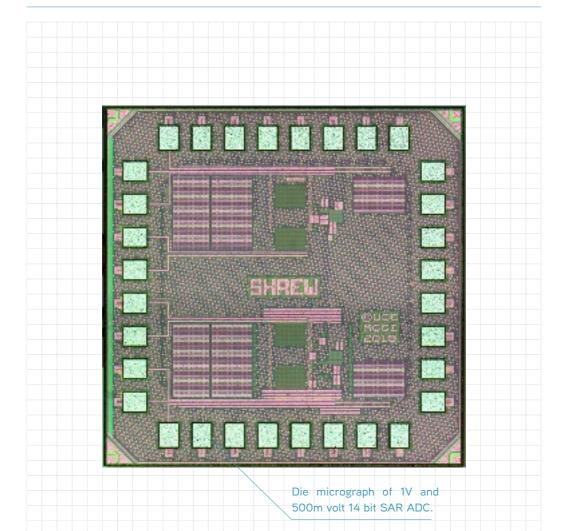

Current Project research: 1.5GHz / 16Bit Noise Shaped SAR ADC on TSMC 28nm

14Bit SAR ADC on TSMC 65nm

DC-DC Converter with Inductor Integration on TSMC 28nm

Research Topics: High-Speed Transceivers, High-Precision Circuit and Power Management.

# Prof. Peter Kennedy

He received his BE (Electronics) degree from UCD in 1984, his MS and PhD from the University of California at Berkeley in 1987 and 1991, respectively, and the DEng from the National University of Ireland in 2010. He joined UCC as Chair of the Department of Microelectronic Engineering in 2000. He served as Dean of the Faculty of Engineering from 2003 through 2005 and as UCC's Vice-President for Research from 2005 to 2011. He moved to UCD in 2017. He has over 400 research publications (including four patents) in the fields of oscillator design, hysteresis, neural nonlinear networks, dynamics, chaos communication, mixed-signal test, and frequency synthesis. He has worked as a consultant for SMEs and multinationals in microelectronics industry and is founding Director of the Microelectronics Industry Design Association (MIDAS Ireland) and the Microelectronic Circuits Centre Ireland (MCCI). He won UCC's Invention of the Year Award in 2011 and led the development of the US-Ireland Research Innovation Awards in 2014/15. He was made a Fellow of the Institute of Electrical and Electronic Engineers (IEEE) in 1998 "for contributions to the theory of neural networks and nonlinear dynamics and for leadership in nonlinear circuits

research and education." He has served as Chair of the IEEE Gustav Robert Kirchhoff Award Committee and a member of the IEEE Fellows Committee. He has received many prestigious awards including Best Paper (International Journal of Circuit Theory and Applications), the 88th IEE Kelvin Lecture, IEEE Millennium and Golden Jubilee Medals, and the inaugural Royal Irish Academy Parsons Award in Engineering Sciences. In 2004, he was elected to membership of the The Royal Irish Academy and was made a Fellow of the Institution of Engineers of Ireland by Presidential Invitation. From 2005 to 2007, he was President of the European Circuits Society and Vice-President of the IEEE Circuits and Systems (CAS) Society (with responsibility for Europe, Africa and the Middle East). He was made a Fellow of the Irish Academy of Engineering in 2014. He was elected to membership of Academia Europaea in 2015. During 2012 and 2013, he was a Distinguished Lecturer of the IEEE CAS Society. He was elected Secretary for International Relations of the Royal Irish Academy in 2012. The following year, his RIA portfolio was expanded to include Policy. He was President of the RIA from 2017 to 2020.

## Luca Avallone, PhD Student

Current Research: Advanced Frequency Synthesis

What's the area of your research? Fractional-N All Digital PLLs.

The key points of the research are: understanding the state-of-theart of the fractional-N structure identifying its main limits and problems; developing a theoretical analysis of fractional-N time-todigital converter (TDC)-based Digital PLLs;implementing a new solution focusing on the TDC.

Education: Bachelor Degree in Electronic Engineering at University of Naples Federico II, 14/03/2014

Master Degree in Electronic Engineering at University of Naples Federico II, 28/09/2017

### Dawei Mai, PhD Student

Current Research: High-Performance Fractional Frequency Synthesis

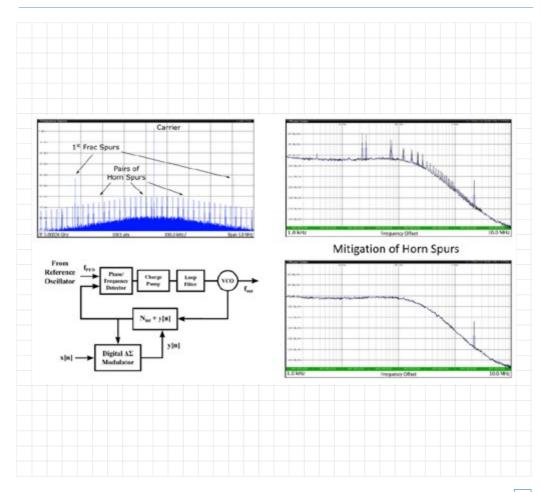

Modelling and analysis of the source of the spurious tones in the fractional-N frequency synthesis are always needed for achieving better communications systems. In the traditional phase-locked loop, the divider controller contributes significantly to the output phase noise. The conventional multistage noise shaping delta-sigma modulator divider controller (MASH-DDSM divider controller) with long input word length will induce periodic and time-varying spurious tones in the output phase noise spectrum. To understand the phenomenon, provide insight into the cause of it, and finally provide solutions to eliminate the periodic tones is the aim of the research.

Other components the traditional analog and digital synthesizers frequency might pose performance limits to the performance of frequency synthesis. For example, the fractional input to the digitally controlled oscillator will introduce noise to the output phase noise. The exploration of those limits is another topic of the research.

#### Research Topics:

- Modelling of frequency synthesizers

- Spur elimination and noise reduction in fractional-N frequency synthesis

Education: Bachelor of Engineering (2015), University College Cork

Master of Engineering (2018), University College Cork

#### Salvatore Galeone, PhD Student

Current Research: RTWOs as multiphase oscillators for frequency synthesisers

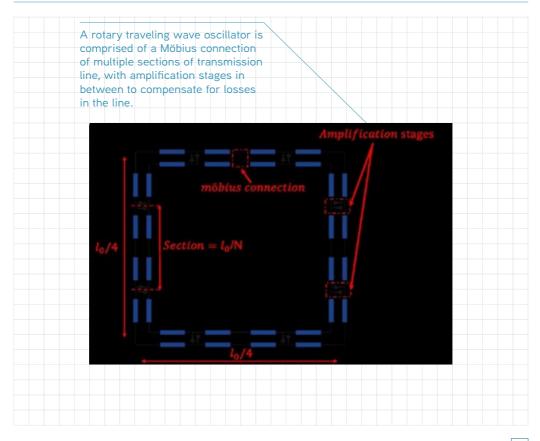

Rotary Travelling Oscillator is an oscillator topology based on a transmission line rather than a lumped resonator. The RTWO operates by propagating a travelling wave along a differential transmission line that is closed in a Möbius connection. The losses of the transmission line are restored by distributed CMOS amplifier stages.

This oscillator topology is attractive for the intrinsic multiphase nature of the oscillator and its ability to operate a very high frequency with low phase noise and power consumption.

Research Topics: Oscillators, phase noise

Education: Salvatore holds Bachelors' degree in Electronic Engineering from University of Pavia, Italy 2009

And Masters' degree in Electronic Engineering from University of Pavia, Italy, 2012

### Dr. Yann Donnelly, Post Doc Researcher

Research: Fractional-N Phase Locked Loops, which employed throughout the communications industry, suffer from the appearance of spurious "spurs", spectral components, which limit performance. This research topic has elucidated the causes of spurs and investigates novel techniques for reducing this unwanted behaviour. Work to date has achieved best-in-class measured spur performance and further improvements are being investigated.

#### Research Topics:

- · PLL phase noise spectrum prediction

- · Reduction of fractional-N spurs by modulator redesign

- · Silicon verification through digital IC implementation

#### Education:

BE (Electrical & Electronic) -University College Cork, 2014

PhD (Microelectronics) - University College Cork, 2018

#### Valerio Mazzaro, PhD Student

Research: Advanced fractional-N frequency synthesizers.

In fractional-N PLLs, increased phase noise and spurious tones come from the interaction between the DDSM quantization error and nonlinearities in the system.

The purpose of this project is to investigate the nature of spurious tones in fractional-N PLLs in order to predict them and, eventually, mitigate them.

Research Topics: Frequency synthesis, fractional-N PLL design, phase noise, spurious tones, horn spurs.

Education: Bachelors Degree in Electronic Engineering at University of Naples Federico II, 2014

Masters Degree in Electronic Engineering at University of Naples Federico II, 2017

# Xu Wang, PhD Student

Current Research: The CMOS device noise from the charge pump (CP) within the phase-lock loop together with other nonlinearity associated with the Fractional-N frequency synthesiser architecture induces spurious response and deteriorates the phase noise performance of the wireless communication system. The current research analytically studies the noise generation mechanism of the CP, the prediction of which is systematically compared with the system nonlinearity noise. Eventually the research aims to come up with novel CMOS

synthesiser design that optimally minimises the phase noise and spurs caused by both the device noise and system nonlinearity.

Research topics: System-andblock-level analogue design for advanced frequency synthesis, Machine-intelligence aided frequency synthesis.

Education: M.Eng. in Electrical and Electronic Engineering at Imperial College London (2015-2019)

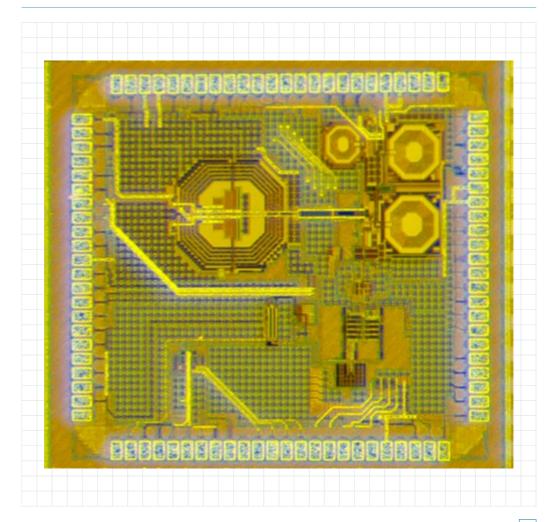

### Prof. Bogdan Staszewski

In Sept. 2014 Prof Staszewski joined University College Dublin (UCD) as a Professor while still holding a part-time Professor position at TU Delft. Prior to 2014, he was at Delft University of Technology (TU Delft) in the Netherlands, where he held academic positions since 2009. He joined TU Delft in 2009 after 18 years in industry with diverse experience in microelectronics and communication systems. He is an IEEE Fellow for contributions to the digital RF communications systems. In 2012, he won the prestigious IEEE Circuits and Systems Industrial Pioneer Award. He has co-authored three books, six book chapters, 170 journal and conference publications. and holds140 issued US patents.

Professional experience: University College Dublin. Position Professor in the School of Electrical, Electronic & Communications Engineering. Carrying out research and teaching in the area of microelectronic circuit design; concentrating on frequency synthesis and RF using advanced CMOS for Internet-of-Things (IoT).

Delft University of Technology (TU Delft), Delft, the Netherlands. July 2009 to present. Carrying out research and teaching in the area of microelectronics, concentrating on frequency synthesis and RF using advanced CMOS.

From 1995 to 2009, he was with TI Dallas, where achievements included the invention and development of the Digital RF Processor (DRP) technology: A novel all-digital frequency synthesizer, all-digital RF transmitter and discrete-time RF receiver architecture that is suitable for the mainstream digital CMOS processes and presents a unique opportunity to build ultra low-cost and power-efficient single-chip radios. Developed a new digitally-intensive CMOS read channel architecture for magnetic recording hard-disk drives. Prior to TI he worked with Alcatel Network Systems, Texas from 1991 - 1995, included work in telecommunications systems, discrete analog and digital circuits, high-speed signal integrity. software algorithms.

Education: Ph.D. in Electrical Engineering, University of Texas at Dallas, USA. Thesis "Digital deep-submicron CMOS frequency for RF synthesis wireless applications," July 2002. M.S. in Electrical Engineering, University of Texas at Dallas, USA, with concentration in digital systems, Dec. 1992. B.S. in Electrical Engineering, Summa Cum Laude, University of Texas at Dallas, USA, with concentration in telecommunications, May 1991.

### Reza Nikandish, Research Staff

Reza received his Ph.D. degree in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 2014. He is a Research Fellow with the University College Dublin, Ireland. Reza was a recipient of the Marie Curie Post-Doctoral Fellowship from the European Union's Horizon 2020 Research and Innovation Program from 2017 to 2020. He was also a recipient of the Iran's National Elites Foundation Fellowship from 2010 to

2014 and the Second-Place Award Winner of the National Electrical Engineering Olympiad in 2004.

#### His current research interests include:

- · CMOS integrated circuits for quantum computing and sensing

- · Energy-efficient AI and machine learning

- · Integrated circuits for mmwave communications

### Amir Bozorg, Post Doc Researcher

Amir Bozorg has been a PhD student at UCD since February 2016. His thesis project is on "mmwave/RF transceiver design". Between Feb. 2017 and Jan. 2019, he was a part-time R&D scientist at S3 Semiconductor, currently Adesto Technology, in Dublin, Ireland, where he developed a K-band phased array receiver. He has received his MSc degree from Amirkabir University of Technology

(Tehran Polytechnic), Tehran, Iran in 2012 in Microelectronics (with Hons.).

#### His research interests are:

- Radio frequency/mmwave transceiver design,

- Discrete-time receiver 2. and filter designs,

- 3. All-digital phase locked loops and frequency synthesizers,

# Feifei Zhang, PhD Student

Current research GHz digital Cartesian RFDAC design

### Research topics:

All digital modulator design;

Class E/F power amplifier design;

FPGA implementation

#### Education:

Joined in Prof. Staszewski's group in Feb. 2017 UCD from Sep. 2014;

MSc of Microelectronics in Beijing University of Technology, China in 2014:

BSc of Navigation guidance and control in Beijing University of Aeronautics and Astronautics, China in 2011

## Dr. Panagiotis Giounanlis, Post Doc Researcher

Panagiotis Giounanlis is a postdoc researcher at UCD since September 2017. His current work includes the development of numerical and analytical approaches for the modeling and simulation of nanostructures and semi-conductor coupled quantum-dots, the development of circuit equivalent electron transfer models for through multiple-quantum-dots, the characterisation and modeling of CMOS devices operation at low temperatures and others. He received his B.SC. degree in Physics and M.Sc. degree - Computational

Physics Master of Science from Aristotle University of Thessaloniki (AUTh), Greece, in 2008 and 2011 respectively . In 2017, he received his Ph.D degree for his research on the modeling of non-linear effects for micro-scale devices (MEMS) and their application to reliability and control by the use of both numerical and analytical approaches. His research interests include: Modeling and simulation of micro/nano-scale devices and mixed-domain complex systems; Solid state Physics; Computational quantum mechanics.

## Viet Anh Nguyen, PhD Student

Current Research: Viet Anh Nguyen is currently researching ultra-lowvoltage, oscillator-based ADCs for Internet of Things applications.

#### Research Topics:

- 1. Analog and Mixed-Signal Integrated Circuit design,

- 2. Analog-to-digital converters,

- 3. Time-to-digital converters,

- Process, voltage and temperature (PVT) tolerant ultra-low voltage design.

Education: Viet Anh Nguyen has been a PhD student at UCD since September 2017. He received his Masters degree in Electronic and Computer Engineering in 2017 and his Bachelors degree in Electronic and Communications Engineering in 2016, both from University College Dublin (UCD), Ireland.

## Suoping Hu, PhD Student

He was born in Changzhou, China. He received the B.E. degree in Integrated Circuit Design and System from Tianjin University (TJU), Tianjin, China, in 2013, and the M.Sc. degree (Hons.) in Electronic Science and Technology from Shanghai Jiao Tong University (SJTU), Shanghai, China, in 2016. He is currently pursuing the Ph.D. degree with University College Dublin (UCD), Dublin, Ireland. Since

2017, he has been sponsored by Analog Device, Cork, Ireland, and worked in a joint project -- ULP receiver.

#### His current interests include:

- Phase-tracking receiver design

- Ultra-low-power receiver design for BLE application.

- Discreet-time circuit design

- Analog/RF circuit design

### Hongying Wang, PhD Student

Current Research: Digital-intensive low-power ADC design with the nanoscale CMOS technology for IoT application and Cryogenic circuit design for the Quantum computer.

#### Research Topics:

- · Digital intensive Level Crossing Sampling ADC design

- · Passive Delta Sigma ADC design

- Single Electron detector design for Quantum Computer

- · Front-end circuit design for cryogenic application

Education: She received her MSc and BSc degrees in Microelectronics from Harbin Institute of Technology. Heilongjiang Province, China in 2015 and 2013, respectively. She is currently pursuing her PhD degree in Microelectronics at University College Dublin (UCD), Dublin, Ireland.

#### Yizhe Hu, Post Doc Researcher

Yizhe Hu received the B.Sc. degree (summa cum laude) in microelectronics from Harbin Institute of Technology (HIT), Harbin, China, in 2013, and the PhD degree in microelectronics from University College Dublin (UCD), Dublin, Ireland, in 2019. He is currently working as a postdoctoral researcher with Prof. R. Bogdan Staszewski in UCD. From 2013 to 2014, he was with Fudan University, Shanghai, China, where he was involved in RFIC design as a postgraduate

researcher. From May 2016 to Oct 2017, he was consulting for the PLL Group of HiSilicon, Huawei Technologies, China, designing 16 nm DCOs and ADPLLs. Since June 2018, he has been consulting for the Mixed-Signal Design Department, TSMC, for a new type of PLL design. His research interests include RF/mm-wave integrated circuits and systems for wireless communications. Dr. Hu has served as a frequent reviewer for the IEEE JSSC, TCAS-I/II, and TMTT.

## Dennis M. Andrade Miceli, PhD Student

Research: Dennis Andrade-Miceli has been a PhD student at UCD since July 2016. His current research work is the framework of Quantum Computers particularly focused on FD-SOI devices modelling under cryogenic operation and ULP digital circuits. Other topics also covered along his research project are LDO, TDC, PVT compensation techniques, and Test automation. He received his MSc degree in Electronic Engineering in 2002 from National Institute of Astrophysics, Optics and Electronics (INAOE), Puebla, Mexico with the project Low-power pipelined ADCs. He received his BSc degree in Industrial Electronic Engineering from Veracruz Institute of Technology, Veracruz, Mexico, in 1998. He has held Electronic Engineering positions in Mexican Maritime Transportation (TMM); research staff in UCD and BarcelonaTech; and R&D Electronic Engineering positions in Arquimea, Intel Labs, and currently in Equal1 Labs.

#### Research Topics:

- FD-SOI Modeling (BSIM, EKV, Verilog-A)

- Cryogenic Electronics

- Quantum Computing

- ULP (sub-Vt) Digital Circuits

- PVT compensation/mitigation on ULP digital circuits

Education: Ph.D. Candidate University College Dublin, Dublin, Ireland 2016 to present

Third level courses in Electronic Engineer Engineering and Junior Research Certification by Technical University of Catalonia. Barcelona, Spain. 2007 - 2011, 2013 - 2014

M.Sc. Electronic Engineering, National Institute of Astrophysics, Optics and Electronics. Puebla, México. 2000 - 2003 B.E.

## Hieu Minh Nguyen, PhD Student

Research: Hieu Minh Nguyen is now focused on all digital RF Digital-to-Analog Converter and Transmitter for low-band and highband 5G application.

#### Research Topic:

- Switched-Capacitor Power Amplifier (Switching Class)

- Hybrid Data Converter for Transmitter

- All Digital Charged Sharing RFDAC

- · Power Combination network for high-efficiency Transmitter.

- mmW Digital Power Amplifier.

Education: Hieu M. Nguyen received the B.E. degrees, M.E in Electronics and Telecommunication Engineering from Ho Chi Minh City University of Technology in 2014 and 2016, respectively. During 2013-2014, he joined Integrated Circuit Design Research and Education Center where he studied about Analog and RF integrated circuit design. He also received the Award of Best Student in Analog IC Design for the design of 24-Bit Delta Sigma ADC. From 2014 to 2015 he worked as a Teaching and Research Assistant at the Department of Electronics Engineering, Faculty of Electricals-Electronics Engineering, Ho Chi Minh City University of Technology. From 2015 - 2017 He worked as an Analog IC Design Engineer in Uniquify where he focused on the PHY and SERDES system. He is currently pursuing Ph.D. in IoE Laboratory in University College Dublin, his research is focusing on Digital Power Amplifier, RFDAC and RF integrated circuit design. He is also serving as a JSSC and TCAS reviewer.

#### Mohamed Shehata, PhD Student

Shehata Mohamed received his B.Sc. and M.Sc. degrees in electrical engineering from Ain Shams University, Cairo, Egypt in 2009 and 2016 respectively. He is currently pursuing his Ph.D. degree in microelectronics from University College Dublin, Dublin 4, Ireland. From 2009 to 2016, he was with MEMS Vision, Cairo, Egypt as analog/mixed-signal IC design engineer where he was involved in designing of VCOs and PLLs. In 2016, he joined Xilinx, Dublin, Ireland as analog design engineer. Since 2017, he has been with Analog Devices, Limerick, Ireland as an RF design engineer. His current research interests include RF and millimeter-wave integrated circuits and systems for wireless communications and automotive radars. Mr. Shehata has served as a reviewer for the IEEE European Solid-State Circuits Conference (ESSCIRC) and IEEE International Symposium on Circuits Systems (ISCAS) since 2017.

### Ali Esmailiyan, PhD Student

Ali Esmailiyan was born in Isfahan, Iran, in 1990. He received the B.Sc. degree in microelectronics from the Isfahan University of Technology (IUT), Isfahan, Iran, in 2013, and the M.Sc. degree in microelectronics from the University of Tehran, Tehran, Iran, in 2016. He is currently pursuing the Ph.D. degree in microelectronics with the University College Dublin

(UCD), Dublin, Ireland. In 2017, he joined Equal1, California, USA, as an IC Design Intern.

His current research interests include:

- Time-based ADCs

- Cryogenic mixed-signal circuit design for quantum computer applications.

Jianglin Du, PhD Student

#### Current Research:

- Design low-power oscillator, SAR-ADC for BLE application.

- Design low-power wireless frequency synthesizer using reference-sampling digital phase locked loop.

- 3. Design grating coupler for silicon-photonic application.

Research Topics: Low-power PLL Design, low-power receiver system

Education: Jianglin Du received his MSc degree in Physical Electronics and BSc degree in Micro-Electronics from Jilin University, China in 2016 and 2013, respectively. He is currently pursuing his PhD in Mixed-signal Circuits Design for IoT at University College Dublin.

#### Yang Xu, PhD student

Current research: RF power amplifier design for 5G system and beyond, which offers efficiency enhancement at the power backoff and bandwidth extension at the same time.

#### Research topic:

- · Broadband continuous mode power amplifier design

- GaN MMIC power amplifier for 5G system

- High efficiency power amplifier with enhanced performance

Education: She received her MSc and BSc degrees in Electromagnetic Field and Microwave Technology at Harbin Institute of Technology, China, in 2015 and 2013, respectively. She is currently pursuing her PhD degree in the RF & Microwave Research Group at University College Dublin (UCD), Dublin, Ireland.

# Prof. Anding Zhu

Anding Zhu received his Ph.D. degree in electronic engineering from University College Dublin (UCD) in 2004. He has been working in UCD since 2005, first as a Post-doc, then a Lecturer, an Associate Professor and now he is a Professor in the School of Electrical and Electronic Engineering. His research interests are in the area of nonlinear modelling and characterisation of RF circuits and systems with a particular emphasis on digital linearisation of RF power amplifiers for wireless communications. He has published over 100 peer-reviewed papers and received research funding from various sources including awards from Science Foundation Ireland (SFI), European Space Agency (ESA), Enterprise Ireland (EI) and industry donations.

Prof. Zhu collaborates with many universities and international companies. He was appointed as a Guest Research Fellow at University of Aveiro, Portugal in 2006 and worked as a Visiting Scholar at University of California at San Diego (UCSD) in 2007. Prof. Zhu

was undertaking a sabbatical leave working as a Visiting Assistant Professor at Stanford University from January to June 2013. He is currently with the RF & Microwave Research Group at UCD and he is the Director of the IoE2 Lab, a multidisciplinary research laboratory focusing on developing enabling technologies and making scientific breakthroughs for next generation Internet of Things (IoT) and future (5G) communication networks. Prof. Zhu is a Funded Investigator in the SFI Research Centre for Future Networks and Communications -CONNECT, where he is particularly working on physical layer networkaware intelligent radio access nodes in collaboration with Xilinx, Analog Devices, MA-COM and Synopsys.

His current research includes behavioural modelling and digital linearisation of RF power amplifiers, high-frequency non-linear circuit and system simulation, wireless transmitter architectures, RF-DAC, digital signal processing and nonlinear system identification algorithms.

### Mr. Brian Keogh, PhD Student

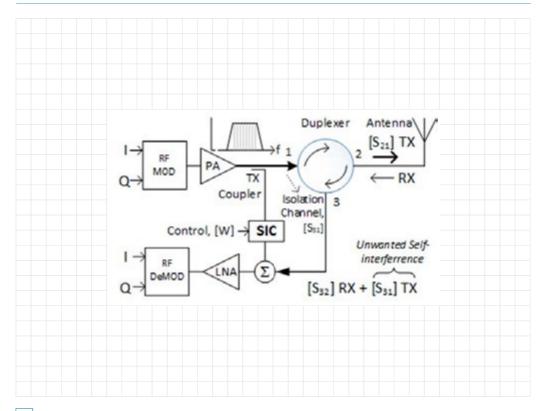

Current Research: Wideband Self Interference Cancellation for 5G Full-Duplex Radio.

Self Effective Interference Cancellation (SiC) is an important consideration for future 5G radio. If it can be successfully implemented, SiC has the potential to double spectral efficiency for certain 5G applications.

Research Topics: Fig. 1 Radio Architecture for Full-Duplex

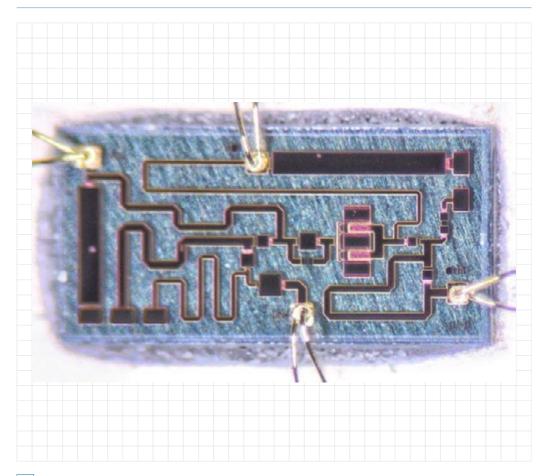

Full-duplex operation is considered difficult to implement because the isolation between the transmit (TX) and receive path (RX) is not perfect. Current solutions take a copy of the TX signal and use this copy to cancel the unwanted selfinterference as shown Fig. 1.